Introduction

GigaDevice released a 32-bit general-purpose MCU based on RISC-V

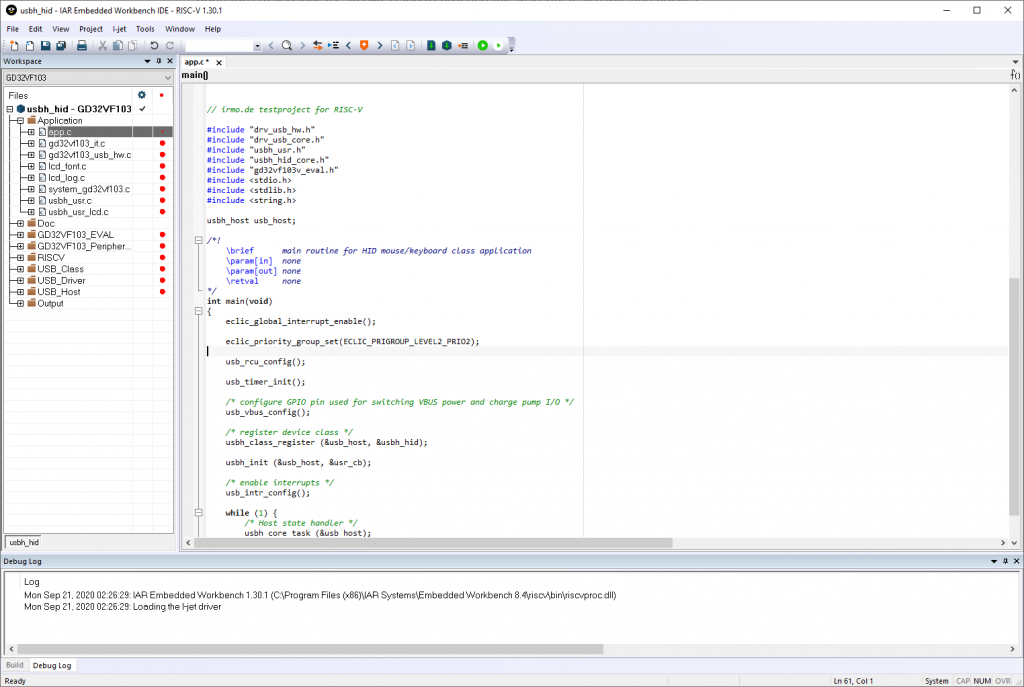

This MCU (and this is real news) in supported by the new IAR workbench for RISC-V. What you get is a complete toolchain including debugger, trance analysis, libraries, simulator and so on.

Let us check in detail if the complete package of hardware and software toolchain can replace the ARM development workflow for embedded applications.

Probably not too many have heard of the Chinese manufacturer GigaDevice. So far, they mostly been known as a SPI NOR Flash memory manufacturer.

A couple of years ago they started making a series called GD32 that is STM32 compatible. The STM32 is one of the most used MCU in embedded applications.

Now GigaDevice released a range of RISC-V-based MCUs: the GD32V series.

Here we get our hands on the GD32VF103. People that are familiar with the Cortex M3 series from ST probably already noticed that this name indicates a replacement product for the STM32F103.

It is therefore a good first step to compare the two SOC architectures first …

Overview GD32VF103

Overview STM32F103

Comparison

At first glance it is obvious that we are seeing a nearly exact clone of the ST architecture here. Even the peripheral bus 2 and 3 divided into two speed classes are identical.

One key difference is marked with 1 in both images. The ARM cortex M3 comes with an NVIC unit for interrupts.

The Nested Vectored Interrupt Controller (NVIC) unit only exists for ARM Cortex M. Its main purpose is to control low latency interrupts with different levels of priority including interrupts from timers like systick.

This unit does not exist for RISC-V out of the box. Here it seems the GigaDevice developers came up with something they call ECLIC for similar functionality.

Unfortunately, there is no documentation about this part. All in all, it looks like GigaDevice extended the Core-Local Interrupt Controller (CLIC) for similar functionality.

The Core-Local Interrupt Controller (CLIC) is not part of the official RISC-V standard. It is only available as an evolving draft in the official github repository.

From the github repository: “The Core-Local Interrupt Controller (CLIC) is designed to provide low-latency, vectored, pre-emptive interrupts for RISC-V systems. When activated the CLIC subsumes and replaces the original RISC-V basic local interrupt scheme. The CLIC has a base design that requires minimal hardware, but supports additional extensions to provide hardware acceleration.”

This should allow similar usage of interrupts but the implementation in silicon is different. So, the vector tables including initialization will be different when used in your code. Watch out for slight difference in power on and reset behavior also.

IAR workbench for RISC-V

Ok it is time to move on. Next, we get in touch with the IAR workbench for RISC-V.

Here are a few example on how simple it is to master some common tasks:

Timers

The first thing I noticed when I tested the evaluation board were the wrong timer delays.

delay_1ms(1);

Does not give us a delay of 1 ms. It is something around 800ns

The solution for this problem is simple.

The examples that come with the default installation are not up to date. Get the latest library from http://www.gd32mcu.com/en/download/7?kw=GD32VF1

and the latest example projects from IAR:

https://github.com/IARSystems/iar-risc-v-gd32v-eval

// Simpel pwm timer timer_deinit(TIMER1); /* initialize TIMER init parameter struct */ timer_struct_para_init(&timer_initpara); /* TIMER1 configuration */ timer_initpara.prescaler = 107; timer_initpara.alignedmode = TIMER_COUNTER_EDGE; timer_initpara.counterdirection = TIMER_COUNTER_UP; timer_initpara.period = 15999; timer_initpara.clockdivision = TIMER_CKDIV_DIV1; timer_initpara.repetitioncounter = 0; timer_init(TIMER1, &timer_initpara);

Interrupts

// simple interrupt for RTC alarm eclic_global_interrupt_enable(); eclic_priority_group_set(ECLIC_PRIGROUP_LEVEL3_PRIO1); eclic_irq_enable(RTC_ALARM_IRQn, 1, 1);

Summary

The great news is, with a STM32F103 design you can try out RISC-V with minimal hardware engineering overhead. Just populate a few boards with the GigaDevice RISC-V MCU and do prototyping and research if you want. With ST you always have an old school ARM fallback solution.

Not sure if it is a good advice to go with the RISC-V MCU in production yet. I did not detect any real showstoppers during my test, but of course I cannot tell anything about long term stability, sourcing, and reliability. And the documentation is not as complete as it should be.

But in my eyes, it is a great and easy step into the world of RISC-V.

Ressources:

Datasheet GigaDevice GD32VF103

http://www.gd32mcu.com/data/documents/shujushouce/GD32VF103_User_Manual_EN_V1.2.pdf

Github CLIC

https://github.com/riscv/riscv-fast-interrupt/blob/master/clic.adoc

IAR example github

https://github.com/IARSystems/iar-risc-v-gd32v-eval

Gigadevice MCU tools:

http://www.gd32mcu.com/en/download/7?kw=GD32VF1

Where is gigadevice producing.

They are a fabless company. Production is at TSMC as far as I know.

I thought TSMC has no capacity

Usually, they do not run on the same line as the latest CPUs. Most MCU are produced in a 40nm process.

I’m used to STM32L4 parts. The power consumption of shown in the datasheet is much higher than I would have expected. Unless I am missing something in my quick read of the datasheet, it consumes 4x as much current as an equivalent STM32L4 part.

An example of how US sanctions on Huawei have been heeded by the whole of Chinese industry. Trump just shot ARM in the head in the world’s biggest electronics market.

Really wish they had QFN-48 available.

Do you know what the IAR workbench costs?

IAR workbench for RISC-V: expect something between 4000€ and 5000€